Отладка встраиваемых систем (Часть 2)

Флагманы: логические анализаторы

Логические анализаторы — сложные приборы. Есть много параметров, которые необходимо оценивать при выборе типа анализатора. Поскольку стоимость такого прибора высока, поэтому целесообразно учитывать требования как разработчиков аппаратной части, так и разработчиков микропрограммного обеспечения, чтобы все потребности ваших специалистов были закрыты одним прибором. Наиболее очевидными характеристиками, интересующими разработчиков оборудования, являются количество доступных каналов (сколько сигналов вы можете отслеживать одновременно), частота дискретизации, уровни напряжения и т. д. Со стороны прошивки важными факторами являются запись в память (миллионы выборок) и методы/способы синхронизации для обеспечения запуска работы прибора в определенный момент выполнения программы. С осциллографами смешанных сигналов вы получаете компромисс между доступным прибором и такими функциями, как память и расширенные возможности запуска.

Режим синхронизации

Режим синхронизации — самая простая операция для понимания. Анализатор имеет внутренний блок генератора, работающий с указанными настройками (обычно выбираемыми пользователем из ряда фиксированных параметров). В каждом внутреннем тактовом цикле прибор производит выборку сигналов и сохраняет данные в памяти. Таким образом, если объем памяти для заданных каналов составляет, скажем, 2 млн сэмплов, а вы сэмплируете с частотой 200 МГц, то максимальный временной интервал будет 10 мс (2 Мб/200 МГц). Данный режим может чрезвычайно полезен для разработки прошивки, но не всегда достаточно времени регистрации данных. Конечно, можно использовать возможности триггера (ждущий режим), чтобы начать захват с нужным интервалом и, таким образом, решить эту проблему.

Режим внешней синхронизации

Этот режим мало чем отличается от предыдущего кроме того, что запускающие импульсы внешние. Выборка выполняется либо по переднему, либо по заднему фронту внешнего тактового сигнала (обеспечиваемого вашей системой). Тогда захваченные сигналы отражают состояние исследуемой системы. Преимущество этого метода в том, что запись производиться по запросу исследуемой системы, что обеспечивает точный выбор времени записи (без сбоев). Так как прибор сэмплирует по фронту/спаду тактового сигнала исследуемой системы, поэтому установка сигнала должна быть окончена, и прибором не будет зафиксировано переходных процессов в виде ложных переходов сигнала. Обычно режим внешней синхронизации имеет половину частоты дискретизации по времени; т.е. если логический анализатор имеет максимальную частоту дискретизации 800 МГц в режиме синхронизации, он может иметь 400 МГц в режиме внешней. Если память прибора 2M и вы сэмплируете с тактовой частотой 20MHz (например, с тактовой частотой процессора), промежуток времени записи будет 100mS. Это в десять раз дольше, чем в режиме синхронизации, описанном выше. В отличие от осциллографов, логические анализаторы имеют гораздо более сложную систему запуска. Система запуска позволяет пользователю написать последовательность событий, которые будут запускать сбор данных. Например, вы можете подсчитать событие 102 раза, прежде чем активируется второй сигнал в течение более чем, скажем, временного интервала в 10 мс, и прошло более 18 секунд, прежде чем инициировать сохранение и начнется запись в память. Или, что еще лучше, вы можете условно записывать сэмплы только тогда, когда происходит желаемое событие триггера. У вас также есть возможность написать еще лучше, вы можете условно записывать сэмплы только тогда, когда происходит желаемое событие триггера. Также, есть возможность написать еще лучше, вы можете условно записывать сэмплы только тогда, когда происходит желаемое событие триггера. У вас также есть возможность написать операторы или даже вернуться в состояние начала записи (сброс), если условие не выполнено.

Дисплей

Все примерно представляют, форму представления сигналов на дисплее логического анализатора. Отдельные сигналы или группы сигналов с помощью шины (объединению в группы) отображаются на временной диаграмме. Подобный способ отображения, также является обычным для программных пакетов разработки внутренней архитектуры ПЛИС (FPGA / CPLD). Однако интерфейс вывода может обладать более специфические функции. Вы можете присвоить группе сигналов логические имена или метки для конкретных значений. Например, у вас может быть имя группы «Задачи» и код 0x06 для «RxCOMM», 0x07 для «TxCOMM», 0x10 для «Таймер» и т. д. Когда шина принимает эти значения, дисплей не показывает значение, а соответствующую метку. Очень удобная функция, поскольку она помогает вам понять ваше представление, вместо того, чтобы пытаться преобразовать биты и байты во что-то осмысленное.

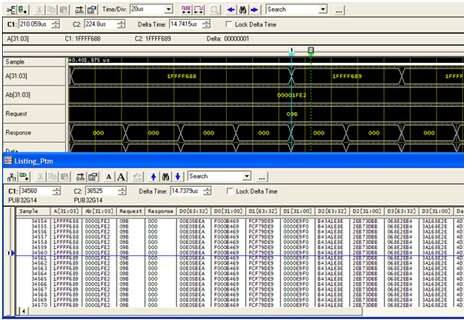

Альтернативным методом отображения данных является режим списка. В этом режиме вы получаете список, каждая строка которого представляет выборку времени. В некоторых случаях это проще всего проследить, особенно если вы используете символическое представление, указанное выше. Режим списка представлен на рисуноке 3.

Рис. 3: Пример сочетания отображения времени и режима листинга

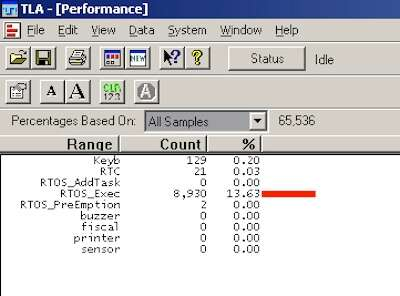

Другим часто предлагаемым режимом отображения является гистограмма, аналогичная рисунку 4. Гистограмма отображает время появления или продолжительности комбинации сигналов (кодов). Если вы назначили комбинации сигналов метки, то получите гистограмму меток. Это эффективно если необходимо анализировать статистические данные работы устройства. Например, вы можете наблюдать за временем выполнения ваших задач или функций.

Рис. 4: Пример отображения гистограммы, отображающей задачи системы

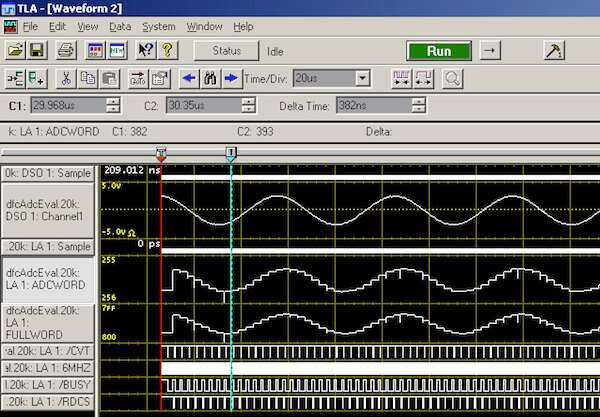

Некоторые приборы предлагают возможность отображать аналоговое представление цифрового сигнала. Если вы выводите на логический анализатор коды, которые представляют значения, записываемые в цифро-аналоговый преобразователь (ЦАП) или считываемые из аналого-цифрового преобразователя (АЦП). Пример отображения аналогового сигнала показан на рис. 5. Верхняя кривая — фактический аналоговый сигнал. Обратите внимание, что этот прибор оснащен цифровым осциллографом выборки (DSO), а также логическим анализатором. Второй след представляет собой оцифрованное слово в аналоговой форме.

Рисунок 5: Пример аналогового представления цифровых сигналов

Внешний триггер

В некоторых случаях для запуска логического анализатора можно использовать внешнее событие. Например, вы можете использовать осциллограф, подключенный к аналоговому или цифровому сигналу, который вы хотите отследить. Вы можете использовать триггерный выход осциллографа для запуска логического анализатора. Подобный способ подключения применяется когда логический анализатор по какой-то причине не имеет доступа к сигналам запуска.

Описание процедуры отладки

Конечно, использование внешних инструментов не отменяет использования других методов отладки, таких как отладчики, ICE и т. д. Инженеры могут свободно комбинировать любые имеющиеся у них методы для выполнения своих задач. Например, в нашей команде успешно используются отладчик с осциллографом смешанных сигналов, чтобы расширить возможности средств отладки. Для начала вам необходимо иметь необходимое оборудование, включая логический анализатор, осциллограф смешанных сигналов, логический анализатор на базе ПК и т. д .

Вам нужно будет найти доступные входы/выходы или выходные контакты исследуемого устройства, чтобы назначить их для выдачи отладочных сигналов. Вы также можете использовать уже задействованные выводы. Например, когда возникла потребность в выводах для отладки над системой с внешним EPROM для данных, мы использовали неиспользуемые комбинации контактов для адреса, который зафиксировал логический анализатор. Например, использование импульса WR для EEPROM без включенного напряжения программирования не повредит EPROM, в то время как логический анализатор может контролировать определенный адрес и захватывать 8-битные данные на шине данных. Таким образом, нашлось необходимое количество выводов. Чем больше у вас свободных выводов, тем легче вам будет выводить данные из вашей прошивки. Поэтому старайтесь закладывать запасные штифты для подключения внешних средств отладки. Разработчики аппаратного обеспечения рекомендуют иметь разъем с несколькими запасными контактами.

После того, мы определили, выводы для подключения средств отладки, необходимо сделать соответствующие макросы отладки, которые обеспечат выдачу тестового сигнала. Поскольку контактов может быть меньше 8, вы не сможете напрямую выводить значения байтов. Вам нужно будет разделить значения на кусочки в зависимости от количества выводов, например, по половине байта, при наличии 4-х линий. Опять же, конкретные потребности и требования будут определять методологию.

Следующим шагом является размещение макросов отладки в проверяемом коде. Это просто, но в зависимости от того, как вы хотите видеть выходные данные логического анализатора, вам может потребоваться обрезать макросы отладки и/или режим захвата логического анализатора.

Следующая часть сложнее. Вы должны настроить свой логический анализатор и решить, какой режим является предпочтительным для сбора данных. Кроме того, это может повлиять на методы создания макросов отладки. Например, если у вас есть режим синхронизации от внешнего сигнала, то вам необходимо будет вывести сигнал стробирования данных. В противном случае этот контакт можно использовать в качестве дополнительного сигнала данных. После этого, вам нужно будет установить свой триггер. Временные зависимости между сигналами зависят от приложения.

Теперь вы готовы запустить систему!

Процедура отладки

Шаг 1. Контакты ввода-вывода

Определите необходимое количество контактов. Вы должны иметь возможность управлять схемой формирования тестового сигнала этих выводов с помощью программного обеспечения. В идеале вы должны предусмотреть возможность подключения запасных контактов к отладочному разъему, который можно использовать для целей отладки. Очень удобно иметь разъемное соединение. Если вы планируете использовать существующие сигналы шины для управления логическим анализатором, вы должны принять во внимание возможные проблемы с целостностью сигнала, которые могут у вас возникнуть. Подключите отладочные выводы к вашему логическому анализатору и отметьте соединения. Не забудьте назначить в настройках анализатора правильный уровень сигнала.

Шаг 2. Макросы и функции отладки.

Для простоты я предположу, что тестируемая система представляет собой однопоточное приложение с прерываниями. Макросы отладки — это код, который формирует необходимые выходные данные отладки. Как вы могли заметить, это не один макрос отладки, а целый набор. В простой версии код примера написан на C и используется в микроконтроллерах PIC. Вы можете легко адаптировать этот код к своей архитектуре.

Сначала вы должны назначить контакты, как показано на рисунке 6.

Рисунок 6: Фрагмент кода для определения макроса ввода/вывода

Здесь мы определяем макросы для каждого контакта. Таким образом, мы можем изменить контакты в будущем.

Затем определим другой макрос, как показано на рисунке 7.

Рисунок 7: Определение макроса отладки

Макрос определяет имя вашей функции отладки и сопоставляет ее с реальной функцией отладки. Отключение макроса CFG_DEBUGLA (установленного в 0) устраняет выходные данные отладки из вашего производственного кода. Кроме того, если вам нужно изменить функцию отладки на другую, вы можете сделать это легко в одной точке.

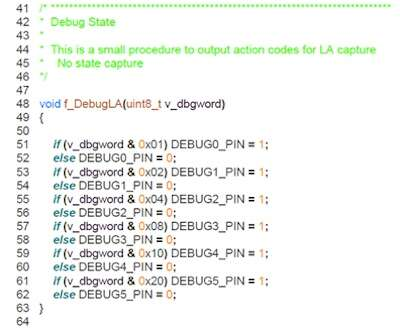

На рис. 8 показана простейшая функция, которая может выполнить эту задачу.

Макрос 1:

Рис. 8: Первый макрос для отправки кодов на ввод-вывод логического анализатора

Макрос принимает байт, но на самом деле использует только 6 бит. Ваша подпрограмма может использовать даже меньше битов. Унифицированный 1-байтовый ввод может сделать этот интерфейс кода общим для проектов, и в каждом проекте у вас может быть разный физический вывод (больше или меньше контактов).

Когда вы вызываете эту функцию, каждый вывод будет принимать свое состояние один за другим. Если ваша распиновка представляет собой запись в один регистр (т.е. один порт), то этот код выше является избыточным. Преимущество приведенного выше кода в том, что он более общий и подходит для разных систем.

Источник: www.edn.com