ТЕХНИЧЕСКИЕ РЕШЕНИЯ НОВОГО ПОКОЛЕНИЯ — ЧАСТЬ 4

Это четвертая статья из серии, в которых исследуется, почему новейшие передовые технологии создания корпусов ИС требуют нового подхода ко всему процессу проектирования — от раннего планирования сборки и прототипирования до создания конструкции, проверки, верификации и подготовки производства. В этих статьях представлена концепция цифрового моделирования: виртуальная модель полного дизайна упаковки, которая позволяет совместное проектирование нескольких инженерных групп на всех этапах разработки.

ВСТУПЛЕНИЕ

В первой статье этой серии мы исследовали новые проблемы, возникающие при использовании корпусов интегральных схем (ИС) и почему моделирование на системном уровне является проверенной методологией проектирования и проверки микросхем с несколькими кристаллами и подложками. Во второй статье мы сосредоточились на многодоменной интеграции, которую обеспечивает методология цифрового моделирования, и обсудили возможности по анализу целостности сигнала, а также, выявление паразитного влияния на имитационной модели. В третьей статье обсуждалась масштабируемость и набор решений, необходимых для текущих и будущих разработок в области ИС, и объясняется, что именно требуется для изготовления ИС на производстве. В этой статье представлены методы, лучшие в своем классе инструменты и возможности тестирования, чтобы инженеры могли более эффективно и быстро достигать золотого стандарта проектирования.

ЗОЛОТОЙ СТАНДАРТ

Золотое стандарт относится к случаям, когда дизайнеры используют средства сборки и тестирования полупроводников (OSAT), утвержденные методики проверки правил проектирования (DRC) и поставляемые PDK / PADK, а также другую документацию, одобренную поставщиком. Например, руководство по правилам проектирования (DRM).

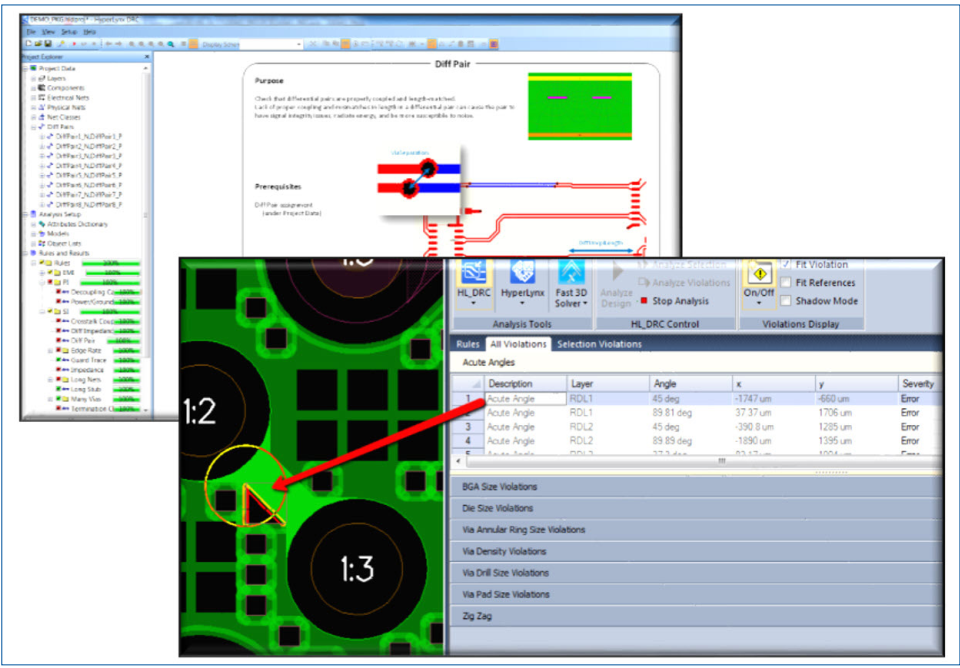

Рис. 1. Интегрированное DRC в проекте может предотвратить ошибки

Для сложных структур ИС золотая стандарт требует гораздо более полного набора проверок; в противном случае общий объем собранных устройств не достигнет поставленных целей годных устройств и превысит запланированные затраты на сборку и испытания. Золотой стандарт должн включать, как минимум: физическую проверку, проверку подключения (также известную как LVS). Такой всеобъемлющий процесс проверки изделия может выявить многие проблемы, требующие доработки. Если эти проблемы оставить без внимания, они могут увеличить время разработки и затраты, а также, привести к срыву производственных графиков. Один из способов предотвратить это — реализовать процесс проектирования «сдвиг влево», выполняемый во время проектирования, чтобы обнаружить и устранить очевидные ошибки проектировщиков на раннем этапе. Использование такой методологии может устранить более 80 процентов ошибок.

ФИЗИЧЕСКАЯ ПРОВЕРКА

Отличительной чертой проверки ИС является использование нескольких специализированных инструментов EDA, что позволяет разработчикам выполнять широкий спектр процедур тестирования. Проверка значительно упрощается, если исходить из того, что каждая отдельная матрица уже проверена на соответствие целевым правилам полупроводникового производства. Также, очень важно обеспечить независимость между средой проектирования и верификации, чтобы гарантировать достоверность результатов верификации.

Проверка содержит DRC правила для проверки взаимодействия между компонентами кристалла (расстояние, размеры элементов и т. д.) и может потребовать отдельного изучения несколько слоев внутри каждого кристалла, чтобы увидеть эти взаимодействия. Физическая проверка включает в себя проверку совмещения на соответствие макету (LVL), коэффициентов масштабирования, а также центров площадок или перекрытий.

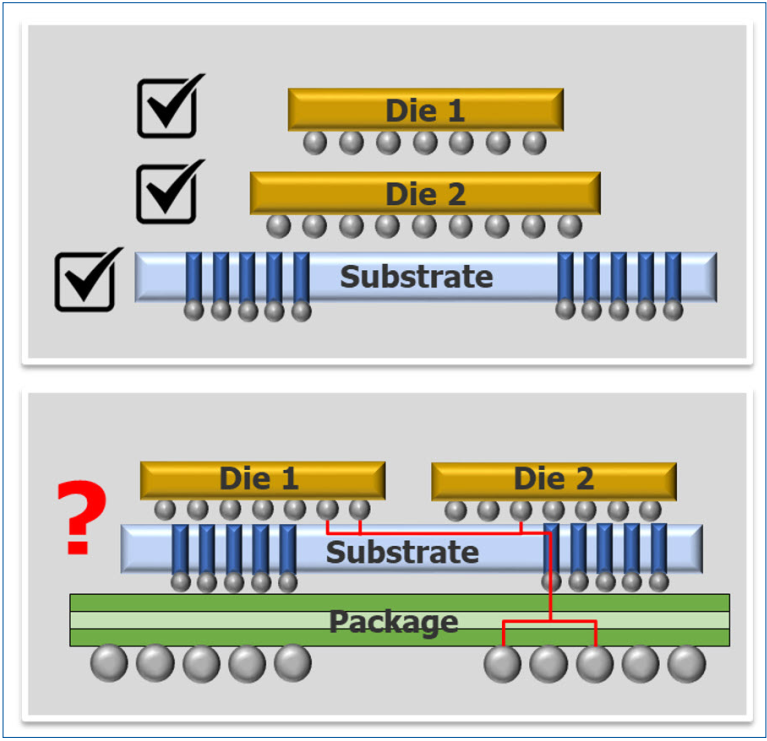

Рис. 2. Одной проверки отдельного кристалла и подложки недостаточно, полная сборка LVL / LVS — единственный способ обнаружить обрывы, короткие замыкания или пограничные соединения, вызванные смещением кристаллов.

Программа EDA должена различать количество слоев и размещение элементов. Используя данные виртуальной модели (цифрового двойника), Mentor’s Caliber ™ 3DSTACK автоматически определяет правильное размещение кристаллов для выполнения проверок DRC и LVL, чтобы убедиться, что конструкция соответствует всем физическим требованиям.

ПРОВЕРКА ПОДКЛЮЧЕНИЯ (LVS)

Проверка LVS в ИС контролирует соединенные элементы и положение выводов, полученные из данных физической компоновки, для создания списка соединений, который сравнивается с эталонным схематическим списком соединений. Проверка подключения выполняется на каждом уровне подложки и между подложками. Автоматизированный пакетный процесс LVS в его простейшей форме должен гарантировать, что данные в формата GDSII содержат информацию о правильном соединении кристалла с кристаллом (для систем с несколькими кристаллами) и кристалла с выводами BGA (для систем с одним кристаллом, так и для систем с несколькими кристаллами).

ПРОВЕРКА ГЕТЕРОГЕННОЙ СБОРКИ

Разнородные сборки 2.5 и 3D обычно включают в себя несколько устройств и несколько подложек для предоставления необходимого решения для масштабирования системы и повышения производительности. С уменьшением расстояния между кристаллом и подложкой, непосредственная близость этих элементов значительно усиливает взаимодействие микросхемы и корпуса, что требует единого процесса совместного проектирования. В случае критических элементов, таких как высокоскоростные интерфейсы или подвидение питания, схемотехническое решение в одной подложке может производить наводки (помехи) на соседние подложки. Разработчики должны найти возможность в совместром проектировании несколькими группами специалистов, используя быстрое прототипирование и совместное проектирование электрических и тепловых характеристик, а также тестирования. Поиск правильного баланса и оптимального решения может представлять собой бесконечный цикл итераций.

Рисунок 3: Совмещение кристаллов и масштабирование

По мере совершенствования методологий и процессов разработчики системного уровня также должны знать, достаточна ли проверка LVL (выравнивание кристалла и упаковки, масштабирование, ориентация и т. д.) и LVS на уровне сборки для обеспечения правильной функциональности и успешного производства гетерогенной сборки.

Необходимость в единой среде, которая позволяет инженерам управлять всеми этими процессами в эффективном, повторяемом и автоматизированном потоке, очевидна. При гетерогенном проектировании и проверке проектировщики должны иметь возможность координировать и управлять несколькими направлениями разработки (проектными базами данных) в одной среде. Имея возможность видеть полную картину (кристалл, переходник, корпус, печатная плата) в одной среде, разработчики могут лучше предвидеть и устранять потенциальные проблемы, связанные с последующим этапом, эффективно выполнять и оценивать компромиссы и сценарии проектирования и четко формировать задачи участникам процесса проектирования.

ТЕСТИРОВАНИЕ

Правильно спроектированная матрица (KGD) является ключом к эффективному тестированию перед укладкой в разнородные 2D- и 3D-сборки. Генерация тестов на уровне пакета также важна — набор тестов должен повторно использовать систему встроенного самотестирования (BIST) и шаблоны сканирования на уровне кристалла. Тестирование граничным сканированием структур межсоединений корпуса гарантирует, что вводы-выводы действительно подключены, и может выявить любые проблемы, связанные с изготовлением подложки или сборкой.

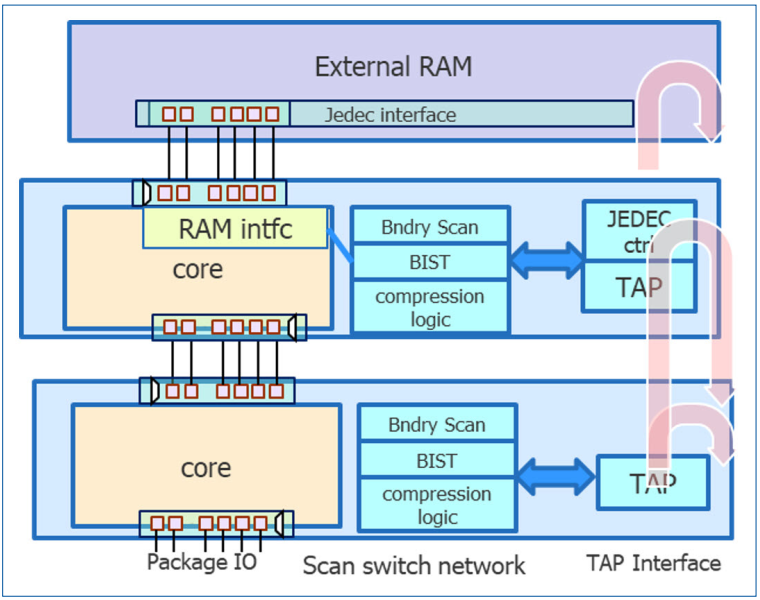

Рисунок 4: Эффективное и действенное тестирование с использованием JTAG TAP, сканирования и тестирования. IJTAG для межкомпонентных соединений «die to die».

Однако даже при качественном тестировании пластин и KGD сборки дефекты могут проявляться из-за повреждения электростатическим напряжением. При упаковке с несколькими кристаллами качество и глубина тестирования пластин имеют решающее значение, если необходимо поддерживать целевой выход годных изделий.

Инструменты тестирования логики Tessent ™ от Mentor предоставляют разнообразные возможности тестирования «передовой практики» для проверки гетерогенных сборок, в том числе:

■ Повторное использование тестовых шаблонов на уровне кристалла

■ Использование общего тестового порта доступа (TAP) для всех уровней подложки.

■ Использование IJTAG для обеспечения гибкости за счет управления режимами тестовых шаблонов

■ Переназначение тестовых шаблонов подложки одного уровня на другие уровни подложки микросхемы.

ЗАКЛЮЧЕНИЕ

В настоящее время скорости передачи сигналов и данных в сочетании с необходимостью уменьшения потребления и тепловыделения требуют, чтобы память была размещена в том же корпусе, что и SoC / ASIC. Интеграция нескольких устройств в одину сборку формирует требования к масштабированию системы, сокращая размеры системы, снижает производственные затраты и часто повышает качество и надежность.

Решения по упаковке нового поколения требуют проверенных, автоматизированных согласований физических, электрических и тепловых характеристик в единой среде разработки, что позволяет инженерам управлять всеми этими процессами в эффективном, воспроизводимом и автоматизированном процессе.

Источник: www.mentor.com