Отладка встраиваемых систем (Часть 1)

Проектирование встраиваемых систем — сложная область. Каждый проект уникален с разнообразными потребностями и ограничениями. В этой статье рассмотрим методы, дадим советы и рекомендации по отладке прошивки встроенных систем с использованием логических анализаторов и цифровых осциллографов. Существует множество способов отладки встроенных систем. Инструменты, которые помогают, включают симуляторы, внутрисхемные эмуляторы, отладчики JTAG/BDM, специальное оборудование, светодиоды и переключатели, а также последовательные или другие коммуникационные порты. В зависимости от бюджета и сложности дизайнеры выбирают необходимые средства отладки, соответствующие их потребностям. Хотя они в первую очередь предназначены для разработки аппаратного обеспечения, вы также можете использовать цифровые или аналоговые осциллографы и логические анализаторы для разработки микропрограмм.

Встроенная прошивка имеет много отличий от традиционной разработки программного обеспечения. Помимо ограниченных аппаратных ресурсов (память, скорость и периферия), встроенные системы всегда имеют параметр времени. Мы часто используем термин система реального времени для описания встроенных систем. Если время отклика не соответствует ожидаемому, то система не считается работающей, даже если функционально она совершенна. Например, если вы управляете каким-либо возбуждением, например двигателями, будет непросто остановить вашу программу и выполнить код шаг за шагом, чтобы определить проблему. Может быть также непостоянный дефект, возникающий только при работе на полной скорости. Одним из способов поиска подобных неисправностей является использование буфера трассировки (еще программисты называют «логированием»).

Буфер трассировки записывает действия в буфер памяти. После события вы можете остановить отладчик или собрать данные для анализа через коммуникационный порт (например, UART, SPI, Ethernet). У этого метода есть преимущества. Например, поскольку это решение для прошивки, оно обеспечивает гибкость. Кроме того, вы можете получить доступ к любой внутренней переменной. Однако буферу трассировки требуется память, некоторый код управления, а также, может быть не всегда просто добиться корреляции с внешними аппаратными событиями. Хотя новые процессоры располагают достаточным количеством памяти, которая остается в избытке и не используется приложением.

Другой метод — коды выполнения. Вместо того, чтобы собирать данные в оперативной памяти системы, вы можете отправлять коды во внешний регистр или внешние выводы микроконтроллера и фиксировать выходные данные с помощью логического анализатора. Это решает проблему с памятью, а требуемый код очень мал и быстр. В этом случае ограничениями являются выходные контакты и объем памяти внешнего прибора. К счастью, синхронизация событий проста в реализации, и у вас есть достаточно продвинутые функции запуска, если используется относительно современный логический анализатор. Подобные методы рассмотрим подробнее в статье.

Отладка программного кода с помощью логического анализатора

В середине 90-х, нашей команде было поручено разработка системы с двумя устройствами: микроконтроллер для выполнения операций ввода-вывода и микропроцессор, выполняющий код приложения. Команда состояла из двух инженеров по оборудованию и трех инженеров по программному обеспечению. Два микропроцессора обменивались данными через 8-битный порт регистра с защелкой. Главный процессор (приложение) опрашивал ведомый (процессор ввода/вывода). Связь была основана на прерываниях (запросе) и подтверждении со стороны ведомого процессора. Инженеры по аппаратному обеспечению отвечали за аппаратное обеспечение и обеспечивали уровень аппаратной абстракции для приложения. Контроллер ввода-вывода, представлял собой автономную прошивку, взаимодействующую с процессором приложения.

Команда разработчиков программного обеспечения иногда жаловалась, что во время тестирования у них отсутствовал отклик (события) клавиатуры. Как и следовало ожидать, мы (умные инженеры по аппаратному обеспечению) никогда не исследовали проблему, потому что считали, что, вероятно, ошибка была на их стороне. После нескольких месяцев и неоднократных жалоб мы решили разобраться в этом вопросе. Мы использовали внутрисхемные эмуляторы и реализовали буфер трассировки на процессоре приложения. Однако, мы не смогли отследить проблему с помощью программного обеспечения. Каждый из нас пришел к выводу, что программное обеспечение работает так, как и требовалось. Под подозрением оказался межпроцессорный интерфейс, поэтому мы договорились об использовании логического анализатора.

Конкретный прибор имел 4 КБ памяти для хранения данных. Мы быстро прикрепили зонды и начали смотреть на сигналы. Вскоре мы поняли, что памяти не хватило, чтобы исследовать этот вопрос. И что еще хуже, в то время не было другого анализатора с гораздо большей памятью. Пришлось немного нестандартно подойти к вопросу настройки синхронизации прибора. После настройки многоуровневого запуска (примерно из 10 стадий), прибор сработал, и мы обнаружили проблему несмотря на маленькую память прибора. Оказалось, что контроллер ввода/вывода реагировал слишком быстро для процессора приложения.

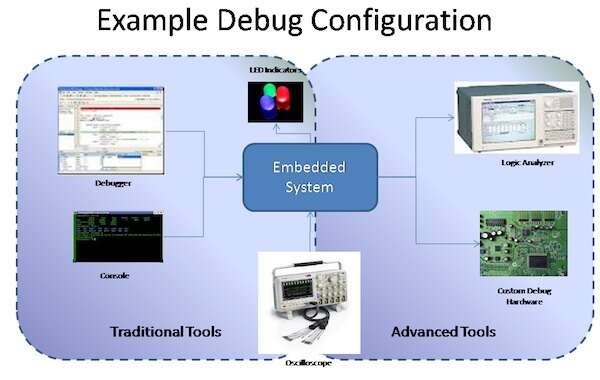

Извлеченные уроки: прошивка обычно имеет много состояний (памяти) и действий, которые коррелируют друг с другом. Вам нужно иметь как можно больше памяти для отладки. Кроме того, для более сложных проблем необходим сложный механизм синхронизации (запуска). На рис. 1 показан пример установки для отладки встроенной системы.

Рис. 1. Пример установки отладочного стенда для встраиваемых систем.

Отладчик и консоли являются наиболее распространенным подходом. Светодиодные индикаторы и переключатели — еще один пример аппаратных средств отладки прошивки. Часто осциллограф используется для решения проблемы синхронизации. Настраиваемое оборудование для отладки может представлять собой микросхемы FPGA или CPLD, которые декодируют некоторые сигналы и предоставляют либо выходные данные осциллографа, либо видимое состояние системы, например, счетчик, отображающий тактовую частоту шины. У многих компаний недостаточно средств для приобретения логических анализаторов. Однако, если он доступен, это незаменимый инструмент отладки. Некоторые инженеры используют очень недорогие логические анализаторы или модули, явно ограниченные в возможностях по сравнению с традиционными логическими анализаторами. Еще одна категория средств отладки — использования логических анализаторов на основе ПЛИС. Они используются в основном для отладки внутри чипа FPGA (например, Xilinx Chipscope). Если на вашей плате есть FPGA, вы можете использовать его для захвата состояния шины. Несмотря на то, что ваша память и возможности запуска будут ограничены, тем не менее, часто это сильно выручает.

Отладка программного кода с помощью цифрового осциллографа

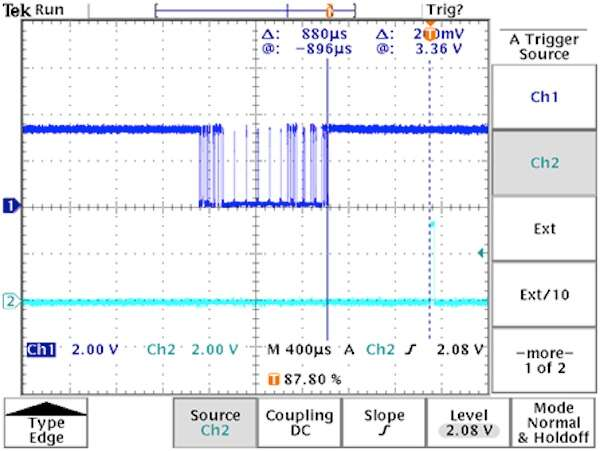

Хотя эта статья в основном посвящена использованию логических анализаторов и отладке встроенного ПО, будет также уместно обсудить распространенный метод использования цифровых осциллографов для отладки. Цифровые осциллографы обладают функцией хранения, необходимая для исследования апериодических или периодических событий. Можно задействовать 1-4 контакта (в зависимости от того, сколько каналов у осциллографа) в определенных точках вашего программного обеспечения в качестве точек прохода. Например, вы можете установить выход при входе в функцию и сбросить выход при выходе. Таким образом, вы знаете, когда ваша функция началась, какова была продолжительность выполнения и когда она закончилась. Вы также можете сопоставить синхронизацию с другой функцией, такой как прерывание или внешнее событие (см. рис. 2).

Рис. 2: Осциллограф, демонстрирующий линию связи и соответствующий ISR

Первая трасса (верхняя, синяя) — это линия связи, а вторая (нижняя, голубая) трасса — это отложенная функция (процедура обслуживания прерывания; ISR), которая обрабатывает событие. Курсор измеряет время между двумя событиями (окончание связи до начала отложенной обработки). Как вы можете заметить, импульс очень мал по сравнению со временем связи. Это означает, что пульс может быть не виден, если процессор достаточно быстр, а масштаб событий велик. Затем вам нужно либо разместить несколько NOP, чтобы увеличить ширину импульса, либо вы можете переключать вывод при каждом выполнении.

Изменение состояния вывода при входе в функцию устойчиво регистрируется осциллографом. Хотя не выявляется информация о продолжительности, но, в данном случае в ней нет необходимости.

Продолжение статьи в следующей части нашего цикла статей.

Источник: www.edn.com